四口2.5G网卡RTL8125B拆机和瓶颈速度测试【图解】

路由知识网原创:文章是关于"四口2.5G网卡RTL8125B拆机和瓶颈速度测试【图解】"的相关知识分享,希望可以帮到大家。 - 素材来源网络 编辑:小易。

一张网卡有四个2.5G网口,接口是PCIe 2.0 x4,有多款,有款乐扩四口2.5G网卡,卖299元,价格不贵,且在京东也有卖,有个15元的全品券,到手284元,平均一个2.5G口71元。很合理!

配有短挡板:

先拆开看看,从硬件上来看后面测试结果,会让你容易明白一些。硬件是基础嘛!

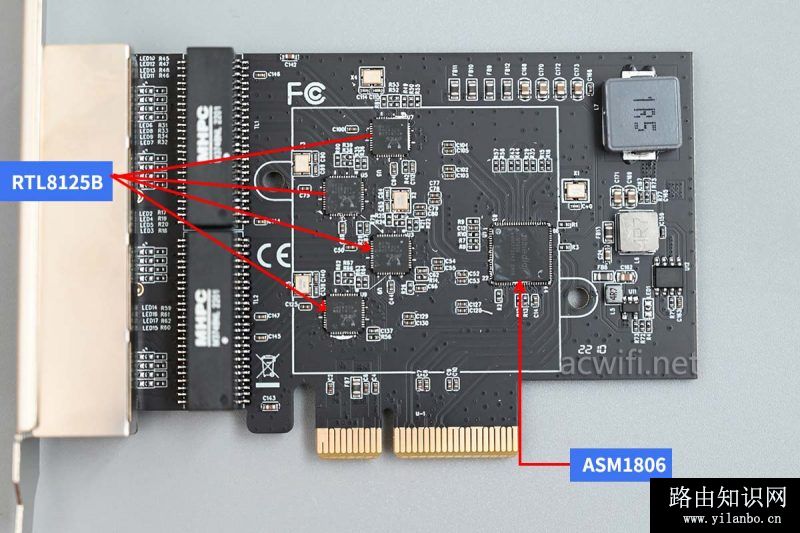

一片正方形的铝散热器,覆盖了所有芯片,其中四颗是2.5G芯片,还有一颗是PCIe通道拆分器,或者叫pcie 交换芯片??

芯片与散热器之间用了带粘性的导热硅脂,所以要捭开散热器就要先用电吹风对它进行加热,然后用力撬起它,要有不怕死的精神。拆东西多了,你就知道要用怎样的手感,专业地说要用多少N·m的力矩。都是心中有数的,要么烂要么不烂,拆不坏的成功是概率很大的,足足有50%之多。

标题都告诉你2.5G网卡芯片是RTL8125B了。

The Realtek RTL8125BG/RTL8125BGS 10/100/1000M/2.5G Ethernet controller combines a four-speed IEEE 802.3 compatible Media Access Controller (MAC) with a four-speed Ethernet transceiver, PCI Express bus controller, and embedded memory.

Supports PCI Express 2.1

Supports 1-Lane 2.5/5Gbps PCI Express Bus

一共有四颗RTL8125B,网卡芯片的背面也有各对应的25Q64CSIG,对应着每颗RTL8125B,所以一共有4颗8MB SPI 闪存,是闪存还是寄存器?

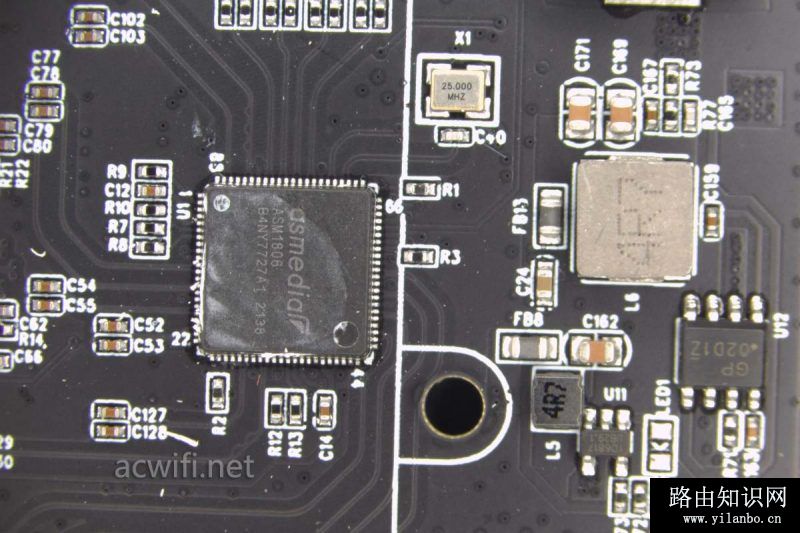

四颗RTL8125B连向这一颗ASM1806:

ASMedia PCIe product ASM1806, a low latency, low cost and low power 6 lane , maximum 4 downstream ports packet switch. With upstream PCIe Gen2x2 bandwidth,ASM1806 can enable users to build up various high speed IO systems, including server, system storage or communication platforms.

参数:

Upstream PCIe interface:

1-, 2- lane PCIe® connecting with root port

Automatic detection of lane configuration on boot-up

Supporting transfer rate of 2.5Gb(250MB/s), 5Gb(500MB/s) per laneDownstream PCIe interface

4 lane PCIe® 2.0 interface supporting up to 4 PCIe® ports

Support L0s/L1/L23/L3 power saving states

Support L1 substate deep power saving mode

Support wake up function in S3/S4

Support port disable by individual control

Support LTR

Support AER

Support SRIS on both upstream and downstream ports.

Max Payload Size = 512Byte

Support hot-plug, surprise remove

从“With upstream PCIe Gen2x2 bandwidth”这里得知,这颗芯片的瓶颈会是PCie 2.0 x2,即500MB/s x2=1GB/s。换算成Gbps就是8Gbps,是这样换算不?我是参考以下资料的。

PCIe 吞吐量(可用带宽)计算方法:

吞吐量 = 传输速率 * 编码方案

例如:PCI-e2.0 协议支持 5.0 GT/s,即每一条Lane 上支持每秒钟内传输 5G个Bit;但这并不意味着 PCIe 2.0协议的每一条Lane支持 5Gbps 的速率。

为什么这么说呢?因为PCIe 2.0 的物理层协议中使用的是 8b/10b 的编码方案。 即每传输8个Bit,需要发送10个Bit;这多出的2个Bit并不是对上层有意义的信息。

那么, PCIe 2.0协议的每一条Lane支持 5 * 8 / 10 = 4 Gbps = 500 MB/s 的速率。

以一个PCIe 2.0 x8的通道为例,x8的可用带宽为 4 * 8 = 32 Gbps = 4 GB/s。

原文链接:https://blog.csdn.net/s_sunnyy/article/details/79027379

四口2.5G网卡的芯片汇总图如下:

背面: